Integrating PikeOS With Microchip’s RISC-V Based PolarFire® SoC FPGA

- Marketing Artimar

- Feb 26, 2024

- 6 min read

This blog post reviews the RTOS developed by SYSGO GmbH, PikeOS, and the process for building and integrating an embedded system with PikeOS and Microchip's PolarFire® SoC FPGAs.

PikeOS: A Versatile Hypervisor-RTOS

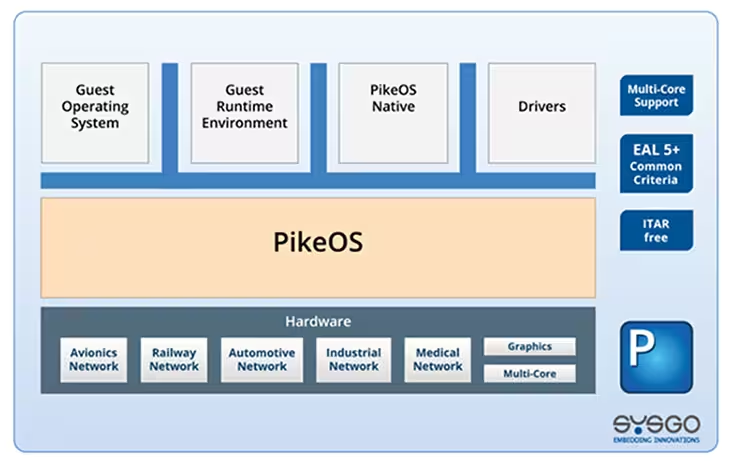

PikeOS, developed by SYSGO GmbH, is a real-time operating system (RTOS) that offers a separation kernel-based hypervisor with multiple partitions for hosting many other operating systems and applications. It has proprietary licenses based on the specific commercial project setup.

PikeOS enables you to build devices for environments with strong demands for safety and security. PikeOS is available for PolarFire® System-on-Chip (SoC) Field-Programmable Gate Array (FPGA) based on RISC-V instruction set architecture (ISA).

PikeOS supports a wide range of guest operating systems, applications, runtime environments and APIs, including ARINC 653 compatible APEX, POSIX, Autosar, other RTOS, various flavors of Linux and many others. Its primary application areas encompass industries with stringent safety and security requirements, such as aerospace, automotive and industrial automation. Therefore, it is certified against the highest levels of these industries such as ASIL-D according to ISO 26262, SIL4 according to EN 50128 and EN 50657, SIL 3 according to IEC 61508 and many more.

This is how SYSGO can help you achieve your company goals. With PikeOS customers can benefit from:

Re-use of legacy code in a Safety-critical environment (separated by the PikeOS hypervisor)

Use low-cost and/or convenient open-source code (drivers, connectivity, libraries) and Linux or Android in a safety-critical environment (separated by the PikeOS Hypervisor)

Mixing of Guest OS like ARINC 653 and POSIX or AUTOSAR and Linux in a certification context (mixed criticality)

Save hardware costs by consolidating several functions in one hardware, using the PikeOS hypervisor

Save hardware costs by efficiently using modern multicore processors (PikeOS can be certified for multi-core)

Save certification time, effort and costs by using commercial-off-the-shelf PikeOS Certification Kits

Save certification costs by utilizing a MILS (Multiple Independent Levels of Safety and Security) architecture, where each application is certified to its individual safety/security level only

Save licensing and certification costs by using PikeOS both for safety and security project requirements

Utilize SYSGO services for time to market, effort and cost optimization (training, consulting, engineering services)

Reduce software obsolescence problems by SYSGO’s long-term support and certification support, supporting long product lifecycles

Secure your software investments as SYSGO’s PikeOS supports many processors (ARM, PowerPC, X86) and offers a broad feature set, allowing you to use it in a wide range of applications covering many different requirements.

This is what you get choosing SYSGO:

SYSGO offers proprietary licenses, as Integration and/or application suits. PikeOS is delivered with the following documents:

Application notes

Optional set of additional drivers suiting the BSP

Access to PikeOS IDE called CODEO for remote debugging, configuration, target monitoring, remote application deployment or timing analysis

Release notes

Installation manual

User Manual

Tutorials

CODEO documentation

Demonstrations

How You Benefit From Microchip’s RISC-V Based FPGA SoCs With RTOS Hypervisor PikeOS

RISC-V is the IT industry's hope for the future. The open architecture has proven itself to be powerful and reliable in matters of self-sufficiency and, moreover, can be used free of charge. For the European location, it is ideally suited to drive digitization without being too dependent on expensive and proprietary technology. SYSGO and Microchip have recognized this and are therefore working together as a hardware-software tandem to offer IoT customers reliable solutions that can be used as embedded systems in almost any industry. As a first step, SYSGO is now developing board support packages for Microchip's PolarFire SoC FPGA family in this partnership.

SYSGO's technology expert Jan Reinhard talks about his experience in developing the Board Support Packages:

“In the vibrant city of Mainz, Germany, the internationally recognized SYSGO, specializing in high-assurance operating systems, identified a seismic shift in technology—the emergence of RISC-V. An open-source hardware ISA based on reduced instruction set computer (RISC) principles, RISC-V promised to redefine the competitive landscape with its efficiency, versatility and transformative performance. Recognizing the potential game-changing technology, SYSGO anticipated a significant business opportunity in RISC-V.”

RISC-V's value proposition resided in its potential to tailor custom cores, thus revolutionizing system designs and enabling a wave of innovative solutions. SYSGO, with its forward-thinking business acumen, understood that harnessing the power of RISC-V would be a significant stride toward future growth.

Acknowledging the strategic importance of collaborations in business, SYSGO sought to build alliances with industry pioneers. The company firmly believed in the concept, "Alone we can do little; together we can do much," especially with the impending RISC-V revolution.

Now, SYSGO is happy to announce the collaborative bond with Microchip Technology, renowned for providing advanced, connected and secure embedded control solutions worldwide. This fruitful collaboration enabled PikeOS to extend its reach to a broader range of devices, enhancing the market position of both SYSGO and Microchip while also promoting the incorporation with RISC-V in the embedded system industry.

The Process

The process of building and integrating an embedded system with RTOS and hypervisor involves several steps, from the initial concept and architecture design to final testing and certification. For this illustration, let's take the example of integrating SYSGO's RTOS PikeOS with Microchip's PolarFire SoC FPGA board using RISC-V ISA.

Define System Requirements: The first step in building an embedded system with an RTOS and hypervisor such as PikeOS involves clearly defining the system requirements. Given that the target environments are mission-critical ones like aerospace, automotive, railway or industrial automation, the system should be designed for real-time performance, reliability, safety and security.

Choose the Hardware Platform: In this case, the selected hardware is Microchip's PolarFire SoC FPGA board, which uses RISC-V ISA. The PolarFire SoC FPGA brings low-power, thermal efficiency and defense-grade security. It is an ideal choice for safety-critical applications.

Refining and Validating the Pre-Existing Blueprint: Once the requirements are defined and the hardware is chosen, the subsequent progression focuses on refining and validating the design of the system for smooth functionality in combination with the RISC-V ISA on the PolarFire SoC FPGA board. This requires a comprehensive examination of the tasks, the mechanisms for task scheduling, the communication and synchronization between tasks, interrupt management and memory handling. Considering PikeOS operates as a partitioned system (hypervisor), an additional layer of inspection involves the study of how various "personalities" or partitions cooperate within the system.

Incorporation and Cohesion: Following the refinement and validation, the subsequent stage underlines the integration of the PikeOS RTOS with the PolarFire SoC FPGA board. This comprises incorporating the right Board Support Package (BSP) exclusively designed for the PolarFire SoC FPGA board, offering device drivers to establish a seamless interaction between PikeOS and the board's hardware elements and amalgamating the newly developed RISC-V core with PikeOS. SYSGO offers a BSP with serial and network support that can be used for the applications. More drivers are available on request.

Testing and Debugging: The BSP is pre-tested and verified to ensure PikeOS runs smoothly on the PolarFire SoC FPGA board and that all tasks and operations work as expected with minimal latency.

Safety and Security Analysis: A critical analysis is performed to ensure that PikeOS on the PolarFire SoC FPGA meets all safety, security and reliability requirements for high-critical environments. This includes worst-case execution timing analysis, fault analysis, penetration testing and security vulnerability assessment.

(Optional) Certification: As the final step, and since PikeOS is certified by regulatory bodies to meet safety standards like DO-178C (for aerospace), ISO 26262 (for automotive) or IEC 61508 (for industry), final certification on a system level can be conveniently done with the aid of SYSGO. PikeOS is a leader in safety or security certification projects. The PikeOS 5.1.3 separation kernel is certified according to cybersecurity standard common criteria at EAL5+, offering an unmatched level of functionality while being extremely secure—thus making it convenient for system integrators to build highly secure embedded systems. This involves exhaustive testing and detailed documentation of all certification artifacts, including requirements specification, design, implementation, testing, traceability and configuration management. The certification must be done on the system level by the final customer, aligned to the system requirements and the components that need certification. PikeOS is certified in a way that the customer can conveniently certify their systems.

In addition to the high-level design process, some technical, PolarFire SoC FPGA specific design decisions are presented in the following figure:

Description:

The firmware (hart 0) starts four application harts with the help of OpenSBI.

Afterward, u-boot starts PikeOS in m-mode. Here, all the functions of OpenSBI can now be handled inside PikeOS. OpenSBI is not needed anymore. Inside the PikeOS we switch from m-mode to s-mode.

The s-mode part then executes the main functionalities of PikeOS.

Microchip’s and SYSGO’s Partnership Helps Accelerate Your Business

This is a broad outline of the development and integration process of PikeOS. The process is carried out hand in hand with customers. Are you interested in learning how we can help you achieve high security within your embedded systems? Contact us for more information.

In the dynamic landscape of technology, SYSGO's strategic alliances illustrate the power of collaboration in embracing and promoting transformative technologies like RISC-V, ensuring businesses are equipped to thrive in a future-ready environment. This new cooperation with Microchip, starting with the PolarFire SoC FPGA board, will now be the first step towards a combined strategy for RISC-V.

Be sure to check out the PikeOS board support package which can be made available by SYSGO.

Simon Jakob, Digital Content Manager at SYSGO GmbH, Nov 14, 2023

Tags/Keywords: Industrial and IoT

Commenti